US010728231B2

# (12) United States Patent

#### Khazan et al.

# (54) DATA SECURITY USING INTER-ZONE GATE CIRCUITS

(71) Applicants: Roger I. Khazan, Arlington, MA (US);

Joshua Kramer, Burlington, MA (US);

Daniil M. Utin, Waban, MA (US);

Mankuan Michael Vai, Sudbury, MA (US); David Whelihan, Framingham,

MA (US)

(72) Inventors: Roger I. Khazan, Arlington, MA (US);

Joshua Kramer, Burlington, MA (US);

Daniil M. Utin, Waban, MA (US);

Mankuan Michael Vai, Sudbury, MA (US); David Whelihan, Framingham,

MA (US)

(73) Assignee: Massachusetts Institute of Technology, Cambridge, MA (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 1362 days.

(21) Appl. No.: 13/937,884

(22) Filed: Jul. 9, 2013

(65) **Prior Publication Data**US 2014/0013123 A1 Jan. 9, 2014

#### Related U.S. Application Data

(60) Provisional application No. 61/669,179, filed on Jul. 9, 2012, provisional application No. 61/669,171, filed on Jul. 9, 2012.

(51) Int. Cl. G06F 21/60 (2013.01) H04L 29/06 (2006.01) H04L 9/08 (2006.01) H04L 9/14 (2006.01)

#### (10) Patent No.: US 10,728,231 B2

(45) **Date of Patent:**

Jul. 28, 2020

# (52) U.S. Cl. CPC ............ H04L 63/061 (2013.01); G06F 21/602 (2013.01); G06F 21/606 (2013.01); H04L 9/0819 (2013.01); H04L 9/0894 (2013.01); H04L 9/14 (2013.01); H04L 63/0428

H04L 9/14 (2013.01); H04L 63/0428 (2013.01); H04L 63/126 (2013.01); H04L 63/20 (2013.01); G06F 21/60 (2013.01); H04L 2209/12 (2013.01)

(58) Field of Classification Search

CPC .... G06F 21/60; G06F 21/62; G06F 21/70–72; G06F 21/74–76; G06F 21/78; G06F 21/82; G06F 21/85; G06F 12/1408; G06F 12/1416; G06F 12/1458; H04L 9/0861; H04L 9/0863; H04L 9/0869

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,473,692 A * | 12/1995 | Davis 705/59         |

|---------------|---------|----------------------|

| 6,138,236 A * | 10/2000 | Mirov et al 726/26   |

| 6,754,819 B1* | 6/2004  | Wootten G06F 21/6209 |

|               |         | 713/150              |

(Continued)

Primary Examiner — Daniel B Potratz

(74) Attorney, Agent, or Firm — Occhiuti & Rohlicek

LLP

#### (57) ABSTRACT

A circuit for secure operation includes a plurality of mutually exclusive circuit zones including a first circuit zone having a first level of security and a second circuit zone having a second level of security less than the first level of security and one or more gate circuits each providing limited transfer of data between the circuit zones, the gate circuits providing all data connectivity between the first circuit zone and the second circuit zone and statically configured to prevent unmodified transfer of data from the first circuit zone to the second circuit zone.

#### 28 Claims, 20 Drawing Sheets

# US 10,728,231 B2 Page 2

#### (56) **References Cited**

#### U.S. PATENT DOCUMENTS

| 6,757,761 B    | 1 * 6/2004  | Smith G06F 15/8007     |

|----------------|-------------|------------------------|

|                |             | 709/215                |

| 6,823,069 B    | 1 * 11/2004 | Kitajima et al 380/44  |

| 8,412,926 B    |             | Gerraty 713/150        |

| 2005/0216726 A | 1 * 9/2005  | Dellmo G06F 21/602     |

|                |             | 713/151                |

| 2005/0216765 A | 1* 9/2005   | Petkus et al 713/201   |

| 2006/0209584 A | 1* 9/2006   | Devadas et al 365/52   |

| 2006/0239458 A | 1* 10/2006  | Bicksler et al 380/221 |

| 2007/0150756 A | 1 * 6/2007  | Kudelski H04L 63/0428  |

|                |             | 713/194                |

| 2012/0311690 A | 1* 12/2012  | Ellis G06F 21/50       |

|                |             | 726/11                 |

<sup>\*</sup> cited by examiner

UNLOCK

$\widehat{\Xi}$

Provision

(13) FIG. 13 006 (12) AES --- KW (E) (Ā) 9996 933 Signing 954 ECDSA (Sign) Keywrap Gen. (1) (8) 904 960c926 SHA 906 AES KW (E) (9) 986 980 946 9096 TRNG (2) SHA 916 982 (10) CEK) Mission Key Metadata CEK(Mission Keys) Zone 1 AES KW (E) Zone 2 Zone 3 966a ₁ Processor 988

Key Unwrap

Key Unwrap

FIG. 17

FIG. 18

# DATA SECURITY USING INTER-ZONE GATE CIRCUITS

### CROSS-REFERENCE TO RELATED APPLICATIONS

This application claims the benefit of U.S. Provisional Applications No. 61/669,171, titled "SHAMROCK: Self Contained High-Assurance Micro Crypto and Key Management Processor," and 61/669,179, titled "Method for Securing Data using Hardware Functional Gates," both filed Jul. 9, 2012, the contents of which are incorporated herein by reference.

# STATEMENT AS TO FEDERALLY SPONSORED RESEARCH

This invention was made with government support under Contract No. FA8721-05-C-0002 awarded by the US Air Force. The government has certain rights in the invention. <sup>20</sup>

#### BACKGROUND

This invention relates to a device and architecture for secure cryptography and key management.

Modern cryptography offers a variety of schemes for the protection of information at-rest on devices and in-transit among devices. A cryptographic scheme typically "scrambles" or "unscrambles" information using a data-permutation algorithm and a short cryptographic key. The 30 security of the scheme depends on the properties of the algorithm and the quality and secrecy of the key. Thus, cryptographic keys need to be created and managed carefully. In particular, keys need to be protected at-rest and in-transit, which itself calls for the use of various cryptographic schemes.

Hardware implementations of cryptographic functions may exist today in hardware, for example as FPGA cores. There may also be special-purpose solutions that are coupled with applications and may implement some form of specialized key management. For example, HAIPE (High Assurance Internet Protocol Encryptor) devices implement a protocol based on the Internet Protocol Security (IPSec) standard for establishing and securing Internet Protocol (IP) communication among devices.

Although many cryptographic schemes have been standardized and implemented efficiently in software and hardware, these solutions are not universally used or embedded in devices. In general, this is the case due to two main reasons:

- a. The lack of generic, easy-to-deploy, and easy-to-use solutions for key management, and

- The challenge of integrating various cryptographic and key management components into a holistically secure design.

While individual cryptographic components exist and may be known to be secure, there is no known "recipe" for integrating different components into secure designs that guarantee security of keys and other information, at-rest and in-transit. It is in such integration that major challenges exist 60 and vulnerabilities are often times introduced.

#### **SUMMARY**

In one general aspect, a self-contained, integrated general- 65 purpose design and architecture for a cryptography and key-management solution can be realized as an integrated

2

circuit core, such as, for example, a Field Programmable Gate Array (FPGA) core or an application-specific integrated circuit (ASIC) core.

The key management tasks may include operations such as creating cryptographic keys, associating keys with their purposes, protecting keys at rest in both volatile and non-volatile memory, making keys available for authorized encryptions and authorized decryptions, delivering keys securely to authorized remote devices, archiving keys, evolving keys with time, retiring keys, etc.

Some implementations attain high performance, low power, flexibility, and extensibility—all at the same time. This is achieved by implementing certain, typically computationally demanding components, such as the standard 15 cryptographic functions, directly in hardware (for example using VHDL), while other components, such as key management protocols, in a higher-level language, such as C, in a softcore micro-controller inside the integrated circuit. The softcore micro-controller, allows for different key management protocols and their extensions to be easily created for and deployed in the architecture, even after the integrated circuit core is manufactured and integrated into an application. The hardware implementations of the cryptographic components used by the application and by the key management components facilitate lower-power, higher-speed operations.

Embodiments of the architecture achieve assured security by separating its internals into a number of physical regions (also referred to as "zones" or "circuit zones" in some examples), and tightly controlling which information flows from one region into another and how it does so. The separation among the different regions is enforced by hardware, through the physical layout of the regions and by their interconnections in the integrated circuit.

In some examples, a device has a dedicated region for storing and handling long-term cryptographic keys of the device (such as the ones used for authenticating the device's identity), another region for storing and handling short-term keys (such as the ones used for securing communication sessions), and yet another region for storing and handling information that does not contain exposed secrets (such as encrypted keys). The only physical paths from a region that handles cryptographic keys to the region that interfaces with the application is by going through a "scrambler" circuit (also referred to as a "gate circuit" or "hardware functional gate" in some examples) such as a secure hash function or an AES encryption function. This restricted physical connectivity completely prevents a possibility of keys inadvertently leaking out due to a logical control flow problem in 50 the design.

The hardware-enforced separations among the regions greatly simplifies the task of establishing and verifying security properties of the design and reduce the possibilities of a design bug or an attack compromising these security properties. In contrast, logical separation of regions, which uses logical "guards" to control and restrict the flow of information among the regions, leaves the regions physically connected and, thus, at some level, allow for a possibility that a malfunction or an attack will lead to an undesired flow of information from one region to another, and to a security problem.

Key management operations often involve coordinated processing in different regions, with information flowing among them. In some examples, the key management component allows for such coordinated processing and the necessary flow of information to occur, despite the physical separations among the regions.

The physical separation of the regions that handle keys from those that do not allows for the latter types to use memory that is external to the integrated circuit. Such external memory may be less expensive than and not be as much size-limited as the integrated circuit's internal 5 memory. The device can protect confidentiality and integrity of the information placed in the external memory with encryption.

In some aspects, hardware functional gates include Elliptic Key Diffie-Hellman cryptography gates, true and pseudorandom number generators, signature verification gates, signing gates, Message Authentication Code (e.g., HMAC) gates, and so on.

In some aspects sensors, cameras, and other external hardware devices can be arbitrarily assigned to a security 15 zone.

In some aspects, the general term "cryptographic processing" relates to cryptographic operations such as encryption, decryption, digital signing, digital signature verification, secure hashing, key generation, and so on.

In another aspect, in general, a circuit for secure operation includes a number of mutually exclusive circuit zones including a first circuit zone having a first level of security and a second circuit zone having a second level of security less than the first level of security; and one or more gate 25 circuits each providing limited transfer of data between the circuit zones, the gate circuits providing all data connectivity between the first circuit zone and the second circuit zone and configured to prevent unmodified transfer of data from the first circuit zone to the second circuit zone.

Aspects may include one or more of the following.

Each gate circuit may implement a function defined by its circuit to process input data and provide output data via interfaces, each of the interfaces located in a single corresponding circuit zone of the plurality of circuit zones. The 35 function implemented by at least some of the gate circuits may include a cryptographic procedure utilizing a cryptographic key. Each of the one or more gate circuits may follow a design that enforces a security policy with the interfaces located in the corresponding circuit zones to 40 prevent unmodified transfers of data between at least some of said circuit zones. The one or more gate circuits may include one or more of an encryption gate circuit, a controlled transfer gate circuit, a decryption gate circuit, a signing gate circuit, a secure hash function gate circuit, and 45 a public key generation gate circuit. Each circuit zone of at least some of the circuit zones may include a memory local to that circuit zone, wherein at least some of the gate circuits include an interface for accessing memory locations in said memory.

The gate circuits may include an encryption gate circuit configured to accept a key via a first interface in the first circuit zone, to accept unencrypted data via a second interface, and to provide encrypted data via third interface in the second circuit zone. The gate circuits may include a decryp- 55 tion gate circuit configured to accept a key via a first interface in the first circuit zone, to accept encrypted data via a second interface in the second circuit zone, and to provide decrypted data via a third interface in the second circuit zone. The first circuit zone may include a key generation 60 circuit for generation of a key value without disclosure of said key value to the second circuit zone. The device may be configured to use a key value provided to a gate circuit to encrypt data in at least one of the first circuit zone and the second circuit zone to provide corresponding encrypted data 65 to the second circuit zone without disclosure of the key value into the second circuit zone.

4

The device may be configured to use a key value provided to a gate circuit to decrypt data in the second circuit zone to provide corresponding decrypted data to the first circuit zone without disclosure of the key value into the second circuit zone. The circuit may include a key initialization circuit comprising at least one of a non-volatile storage in the first circuit zone, a Physical Unclonable Function (PUF) in the first circuit zone, and port for passing a value from outside the device to the first circuit zone. The device may include a programmable processor located outside the first security zone, wherein the circuit is configured to validate software for controlling the processor according to key values stored in the first circuit zone. The device may include a Field Programmable Gate Array (FPGA) configured according to configuration data to implement circuit zones and gate circuits. The device may include an Application Specific Integrated Circuit (ASIC).

In another aspect, in general, data stored on a non-transitory computer readable medium includes configuration instructions for configuring a circuit having a plurality of mutually exclusive circuit zones including a first circuit zone having a first level of security and a second circuit zone having a second level of security less than the first level of security and one or more gate circuits each providing limited transfer of data between the circuit zones, the gate circuits providing all data connectivity between the first circuit zone and the second circuit zone and configured to prevent unmodified transfer of data from the first circuit zone to the second circuit zone.

Aspects may include one or more of the following features.

The configuration instructions may include hardware description language (HDL) instructions. The configuration instructions may include instructions for configuring a Field Programmable Gate Array (FPGA).

In another aspect, in general, a method for operating a device having a first circuit zone having a first level of security and a second circuit zone, mutually exclusive from the first circuit zone and having a second level of security less than the first level of security includes maintaining data in the first circuit zone, providing first data in the first circuit zone to an interface in the first circuit zone to a first gate circuit, the first gate circuit coupling the first circuit zone and the second circuit zone, processing the first data in a first gate circuit to produce second data, providing the second data from the first gate circuit through a second interface in the second circuit zone, wherein the first gate circuit is configured by its circuit design to process the first data to produce the second data such that disclosure of the second data does not disclose of the first data.

Aspects may include one or more of the following features.

Processing the first data in the first gate circuit to produce second data may include forming the second data according to a cryptographic procedure according to a key value in the first data. The cryptographic procedure may include at least one of an encryption procedure, a signing procedure, and a public key generation procedure. Processing the first data in the first gate circuit to produce second data may include forming the second data as a secure hash of the first data.

The method may further include maintaining third data in the second circuit zone, providing the third data in the second circuit zone to a third interface in the second circuit zone to a second gate circuit, the second gate circuit coupling the first circuit zone and the second circuit zone, processing the third data in a second gate circuit to produce fourth data, providing the fourth data from the second gate

circuit through a fourth interface in the first circuit zone, wherein the second gate circuit is configured by its circuit design to process the third data to produce the fourth data such that disclosure of the fourth data does not disclose the third data.

Processing the third data in the second gate circuit to produce fourth data may include forming the fourth data according to a decryption procedure according to a key value in the first circuit zone.

In another aspect, in general, a method for operating a secure device having a plurality of mutually exclusive circuit zones, including a first circuit zone having a first level of security and a second circuit zone having a second level of security less than the first level of security, the method 15 includes unpacking a key exchange package, the unpacking including receiving a key exchange package in the second circuit zone, the key exchange package including encrypted key data and processing the encrypted key data using a content key in the first circuit zone to generate decrypted key 20 data and storing the decrypted key data in the first circuit zone without disclosing the decrypted key data into the second circuit zone.

Aspects may include one or more of the following features.

The key exchange package may include header data and the method further comprises processing the header data to generate the content key and storing the content key in the first circuit zone without disclosing the content key into the second circuit zone. The key exchange package may include 30 encrypted key associated data and the method may further include processing a data item in the first circuit zone with a non-invertible function to generate a modified data item and storing the modified data item in the second circuit zone, and processing the encrypted key associated data using the 35 modified data item to generate decrypted key associated data and storing the decrypted key associated data in the second circuit zone. The data item may include the content key.

The method may further include cryptographically prokey data without disclosing the decrypted key data into the second circuit zone. Cryptographically processing the data may include encrypting the data into the second circuit zone using the decrypted key data. Cryptographically processing the data may include decrypting the data into the second 45 circuit zone using the decrypted key data. The secure device may include a plurality of gate circuits providing limited transfer of data between the circuit zones, the gate circuits providing all data connectivity between the first circuit zone and the second circuit zone and preventing unmodified 50 transfer of data from the first circuit zone to the second circuit zone. Processing the encrypted key data using the content key to generate decrypted key data may include using a decryption gate circuit to decrypt the encrypted key data using the content key.

Processing the data item to generate a modified data item may include using a secure hash gate circuit to compute a secure hash of the data item. Processing the encrypted key associated data using the modified data item may include using a decryption circuit to decrypt the encrypted key 60 associated data using the modified data item. At least some of the plurality gate circuits providing connectivity between the first circuit zone and the second circuit zone may store data in the first circuit zone. The method may further include performing a cryptographic exchange with another secure 65 device including using a decryption gate circuit to decrypt data received from the other device in the second circuit

zone using the decrypted key data without disclosure of the decrypted key data into the second circuit zone.

The method may further include performing a cryptographic exchange with another secure device including using an encryption gate circuit to encrypt data in the second circuit zone using the decrypted key data without disclosure of the decrypted key data into the second circuit zone. The secure device may include a root circuit zone having a third level of security greater than the first level of security and the second level of security, and processing the header data in the second circuit zone to generate the content key in the first circuit zone includes using a key agreement key in the root circuit zone. Decrypted key associated data may include key metadata associated with the decrypted key data.

In another aspect, in general, a method for operating one or more secure devices, each having a plurality of mutually exclusive circuit zones, including a first circuit zone having a first level of security and a second circuit zone having a second level of security less than the first level of security, the method including processing, at a sending device, key data using a content key to generate encrypted key data and storing the encrypted key data in the second circuit zone without disclosing the key data into the second circuit zone, packaging the encrypted key data into a key exchange 25 package, and transmitting the key exchange package to one or more receiving devices.

Aspects may include one or more of the following feafures.

The method may further include processing, at the sending device, a data item in the first circuit zone using a non-invertible function to generate a modified data item and storing the modified data item in the second circuit zone without disclosing the data item into the second circuit zone processing, at the sending device, key associated data using the modified data item to generate encrypted key associated data and storing the encrypted key associated data in the second circuit zone, and packaging the encrypted key associated data into the key exchange package.

The method may further include processing, at the sendcessing data in the second circuit zone using the decrypted 40 ing device, private key data in the first circuit zone to generate header data and storing the header data in the second circuit zone, and packaging the header data into the key exchange package.

> The one or more secure devices may include a plurality of gate circuits providing limited transfer of data between the circuit zones, the gate circuits providing all data connectivity between the first circuit zone and the second circuit zone and preventing unmodified transfer of data from the first circuit zone to the second circuit zone. Processing key data using a content key to generate the encrypted key data may include using an encryption gate circuit to encrypt the key data using the content key. Processing the data item to generate a modified data item may include using a secure hash gate circuit to compute a secure hash of the data item. Processing the key associated data using the modified data item may include using an encryption circuit to encrypt the key associated data using the modified data item in the second circuit zone. At least some of the plurality gate circuits providing connectivity between the first circuit zone and the second circuit zone may store data in the first circuit

The method may further include receiving the key exchange package in a second circuit zone of a receiving device, the key exchange package including encrypted key data, processing, at the receiving device, the encrypted key data using a content key in the first circuit zone to generate decrypted key data and storing the decrypted key data in the

first circuit zone of the receiving device without disclosing the content key into the second circuit zone of the receiving device. The key exchange package may include header data and the method may further include processing, at the receiving device, the header data to generate a content key and storing the content key in the first circuit zone of the receiving device without disclosing the content key into the second circuit zone of the receiving device.

The key exchange package may include encrypted key associated data and the method may further include processing, at the receiving device, a data item with a non-invertible function to generate a modified data item and storing the data item in the second circuit zone of the receiving device without disclosing the data item into the second circuit zone of the receiving device; and processing, at the receiving device, the encrypted key associated data using the modified data item to generate decrypted key associated data and storing the decrypted key associated data in the second circuit zone. The data item may include the content key.

In another aspect, in general, a method for establishing group key data among a plurality of secure devices, each secure device having a plurality of mutually exclusive circuit zones, including a first circuit zone having a first level of security and a second circuit zone having a second level 25 of security less than the first level of security including receiving the key exchange package in a second circuit zone of each of the secure devices, the key exchange package including encrypted key data, establishing a shared key data in the first circuit zone of each of the secure devices 30 including, for each of the secure devices, processing the encrypted key data using a content key to generate decrypted key data and storing the decrypted key data in the first circuit zone of each of the secure device without disclosing the content key into the second circuit zone of the secure device, 35 securely exchanging messages between the secure devices, the messages being processed by the shared key data.

Aspects may include one or more of the following features

The method may further include distributing the key 40 exchange package from a secure computer server.

In another aspect, in general, a method for computer-implemented verification of security of a device includes accepting data comprising a circuit description of the device, identifying using a computer a plurality of mutually independent circuit zones from the circuit description such that no data paths pass between said circuit zones, identifying a plurality of gate circuits providing data paths between the circuit zones, the gate circuits being verified to limit unmodified transfer of data between zones by their circuitry according to a security policy, and verifying that the security device complies with the security policy according to whether all data paths between the circuit zones are via the identified gate circuits according to the security policy.

Aspects may include one or more of the following features.

The method may further include using a computer to verify that the gate circuits limit unmodified transfer of data between zones by their circuitry according to the security policy. Accepting the circuit description of the device may 60 include accepting a specification of the circuit zones of the device. The method may further include associating a security index with each circuit zone, and wherein verifying that the security device complies with the security policy comprises verifying that the security indices of interfaces 65 between the gate circuits and the circuit zones satisfy the security policy.

8

Other features and advantages of the invention are apparent from the following description, and from the claims.

#### DESCRIPTION OF DRAWINGS

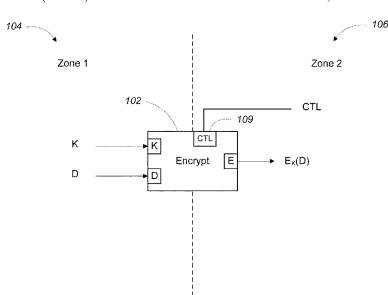

FIG. 1 is a hardware functional gate (HFG).

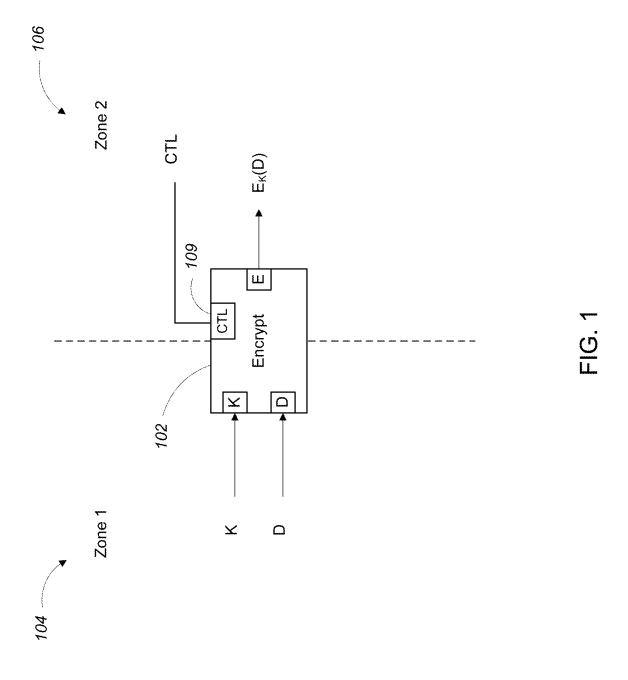

FIG. 2 is first encryption HFG.

FIG. 3 is a controlled transfer HFG.

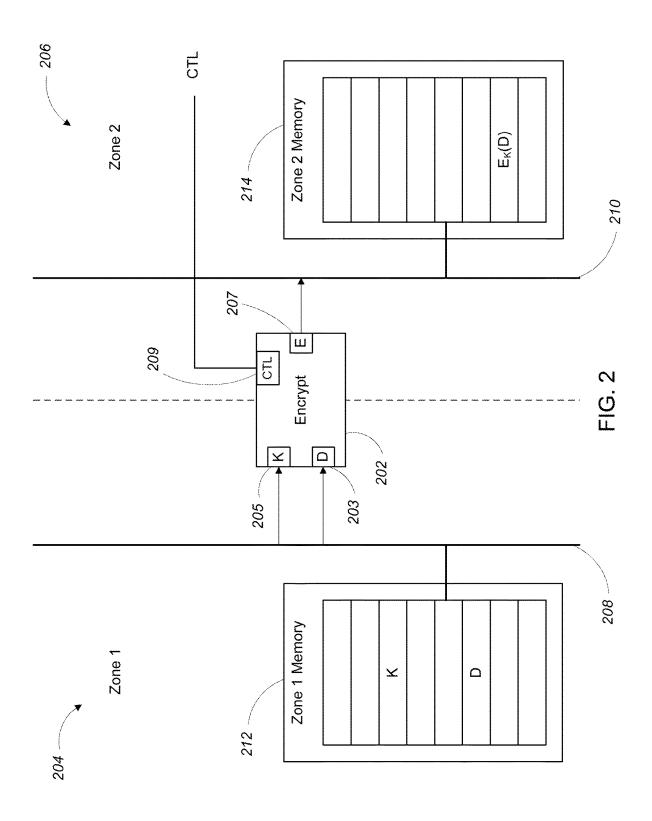

FIG. 4 is a second encryption HFG.

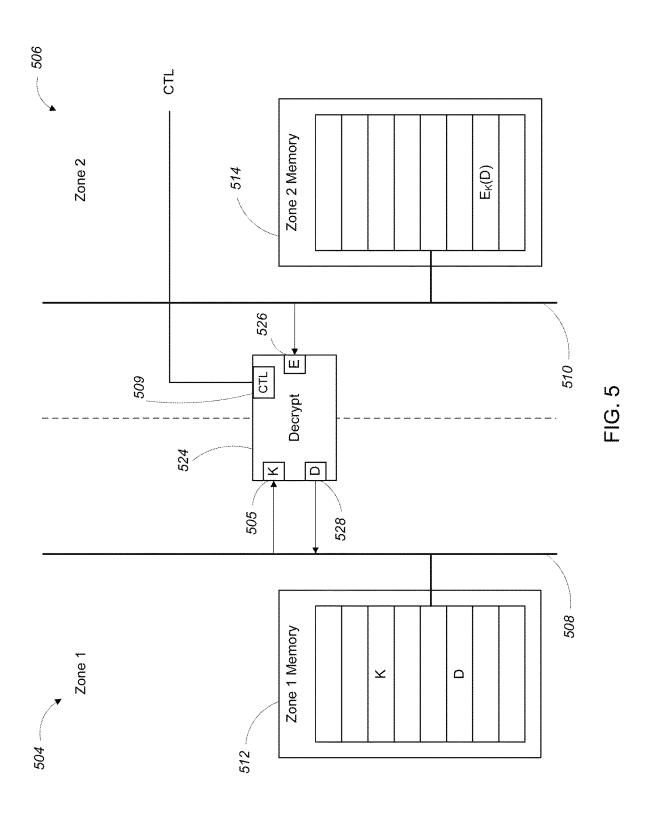

FIG. 5 is a decryption HFG.

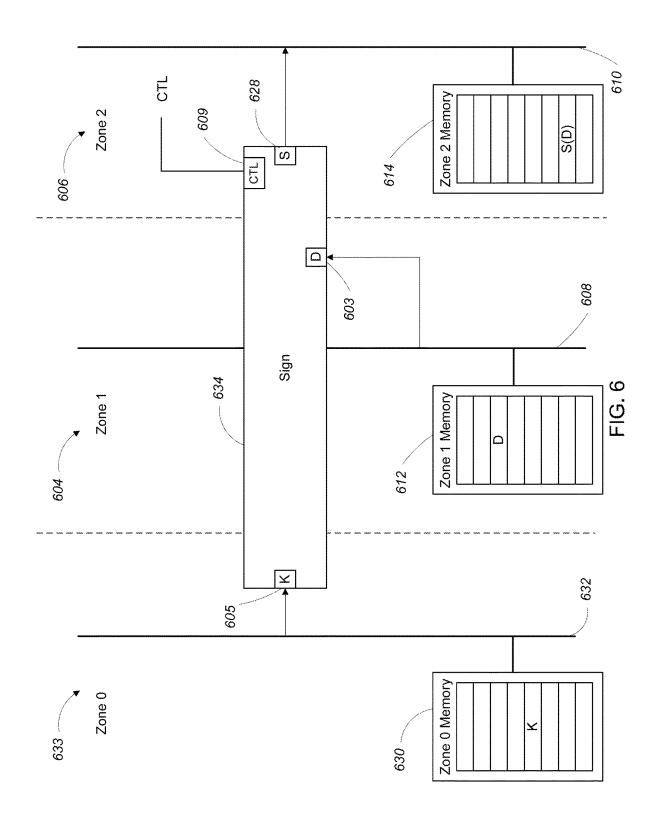

FIG. 6 is a digital signing HFG.

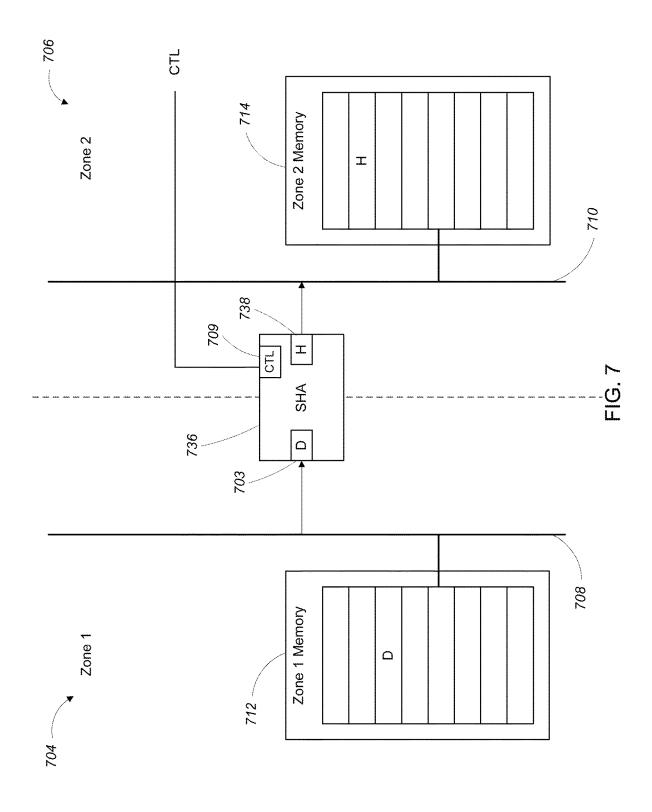

FIG. 7 is a secure hash function HFG.

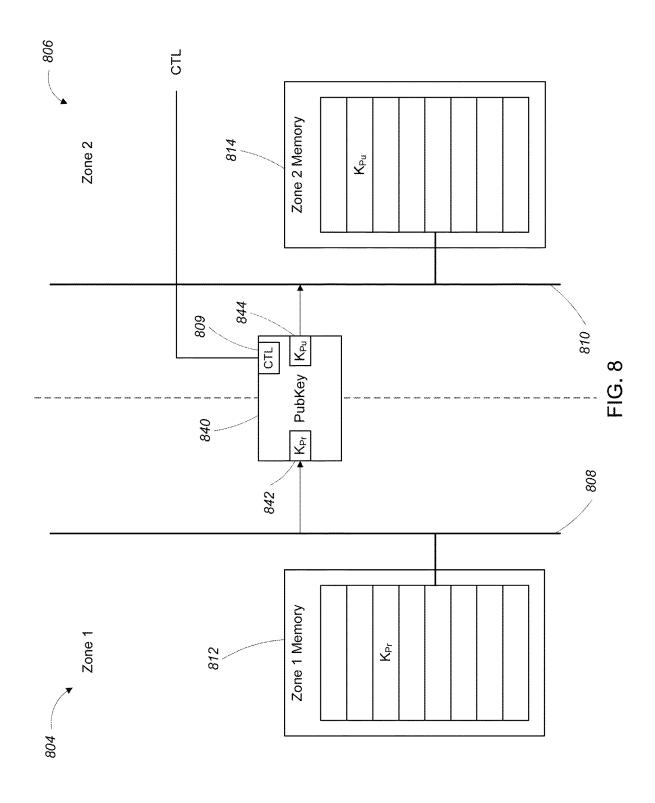

FIG. 8 is a public key generation HFG.

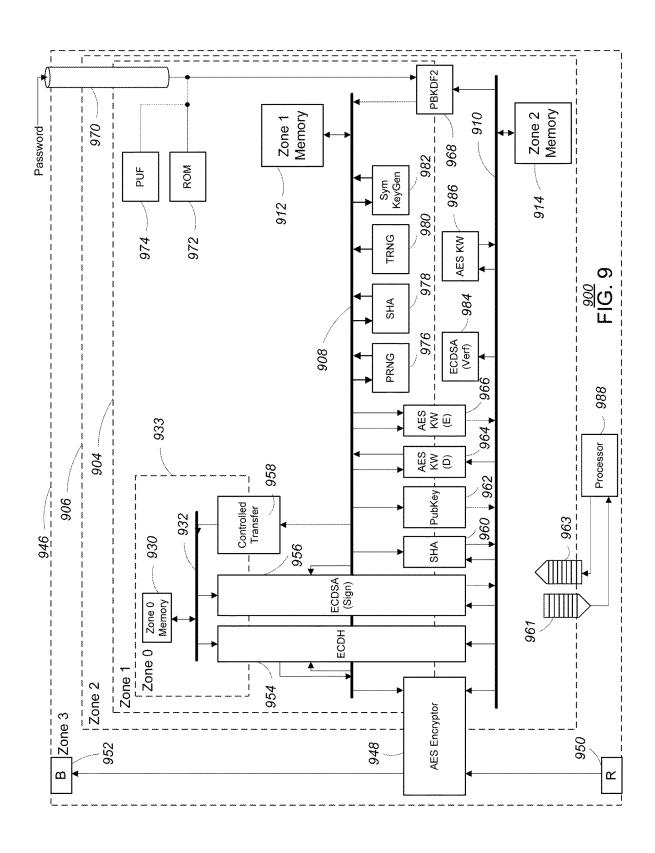

FIG. 9 is a device including a number of HFGs.

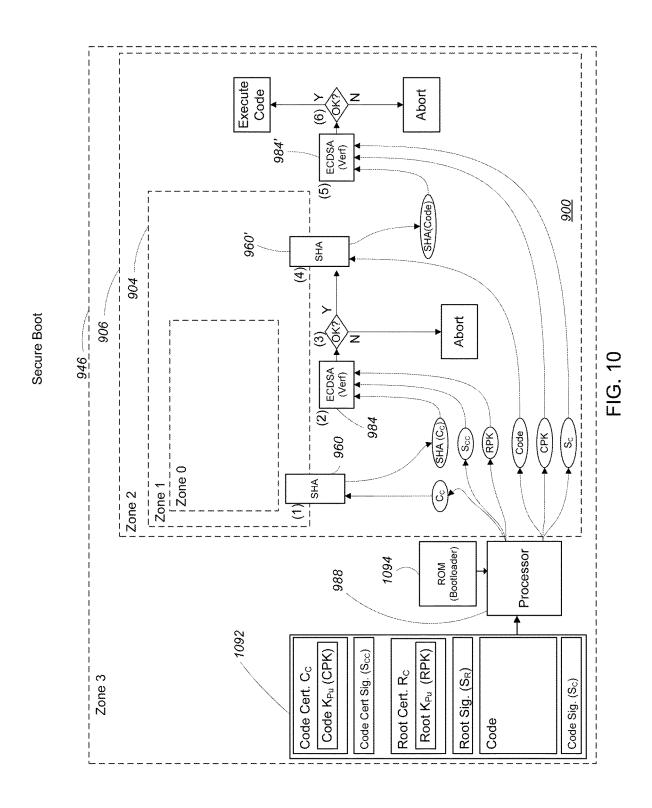

FIG. 10 is a secure boot procedure.

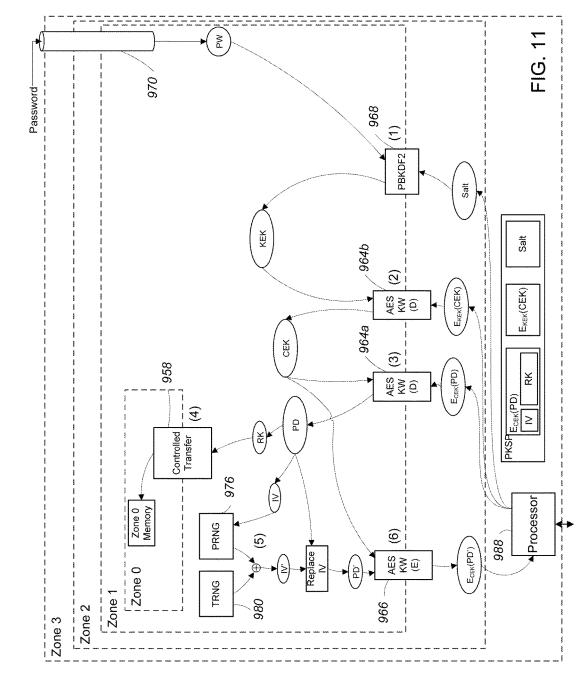

FIG. 11 is an unlock procedure.

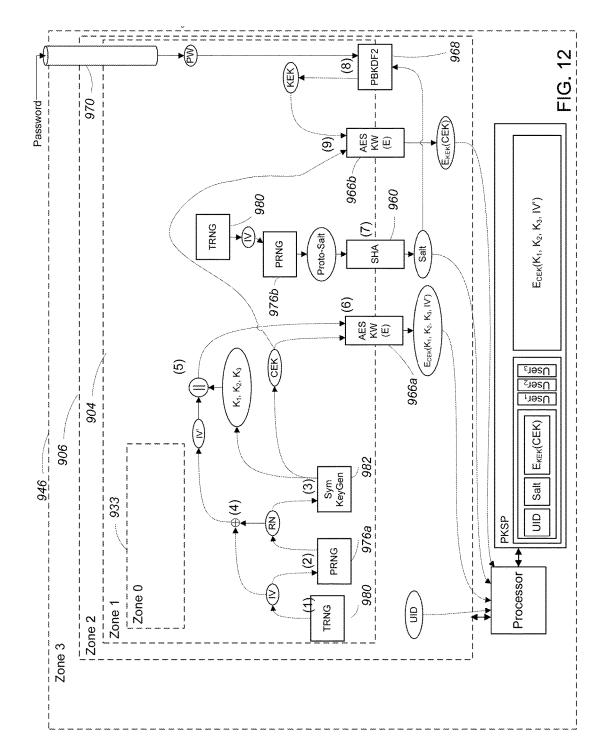

FIG. 12 is a provisioning procedure.

FIG. 13 is a first part of a keywrap generation procedure.

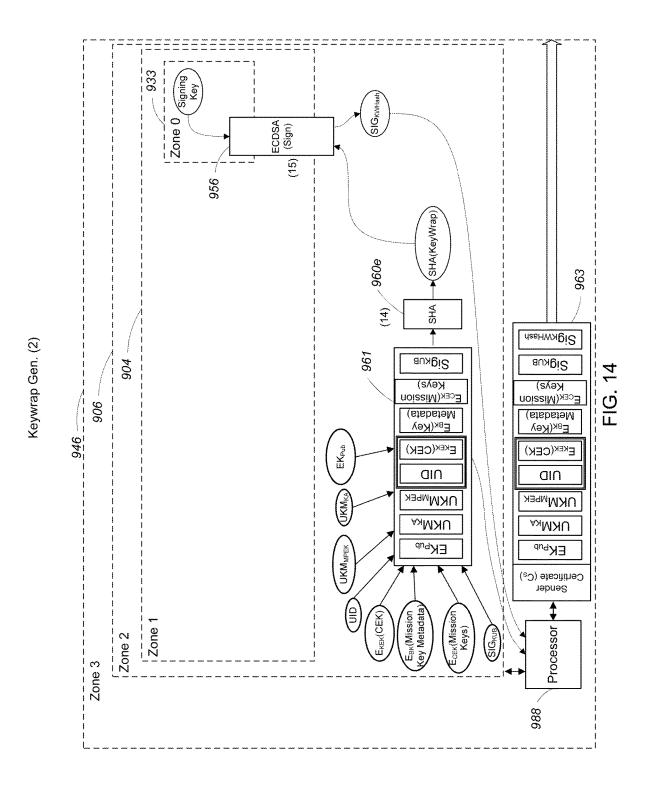

FIG. **14** is a second part of a keywrap generation proce-

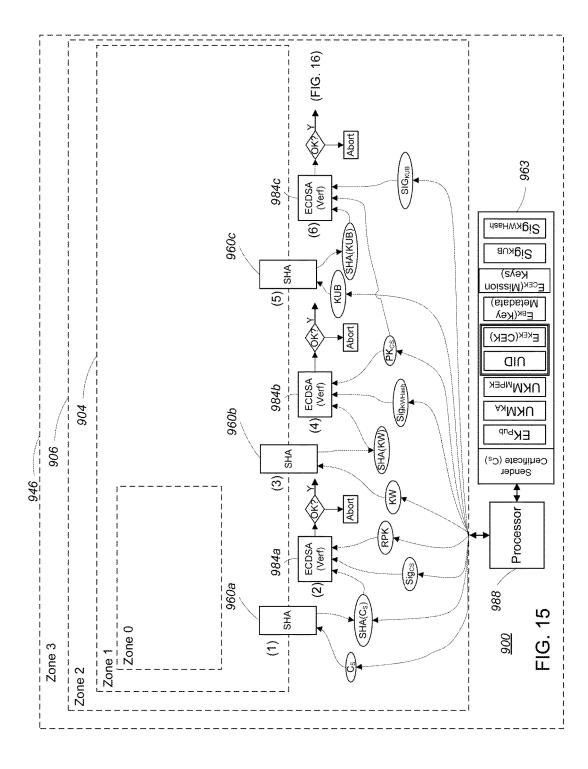

FIG. 15 is a first part of a key unwrap procedure.

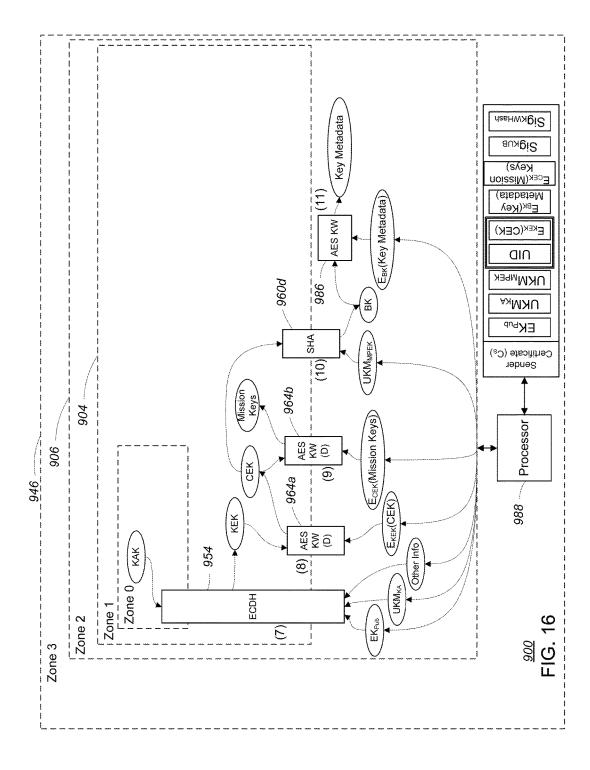

FIG. 16 is a second part of a key unwrap procedure.

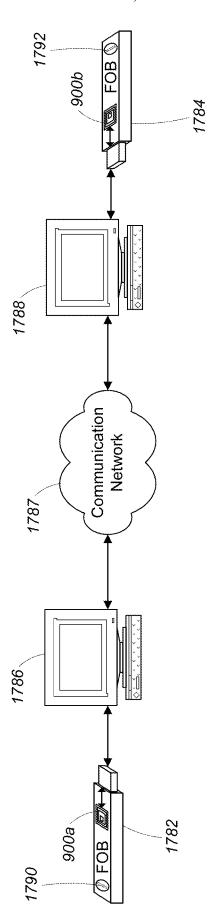

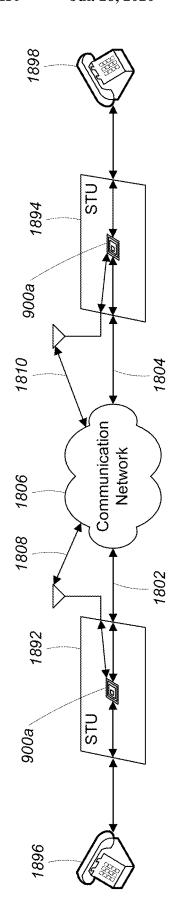

FIG. 17 is a key fob application of a key management and cryptography device.

FIG. 18 is a secure telephony application of a key management and cryptography device.

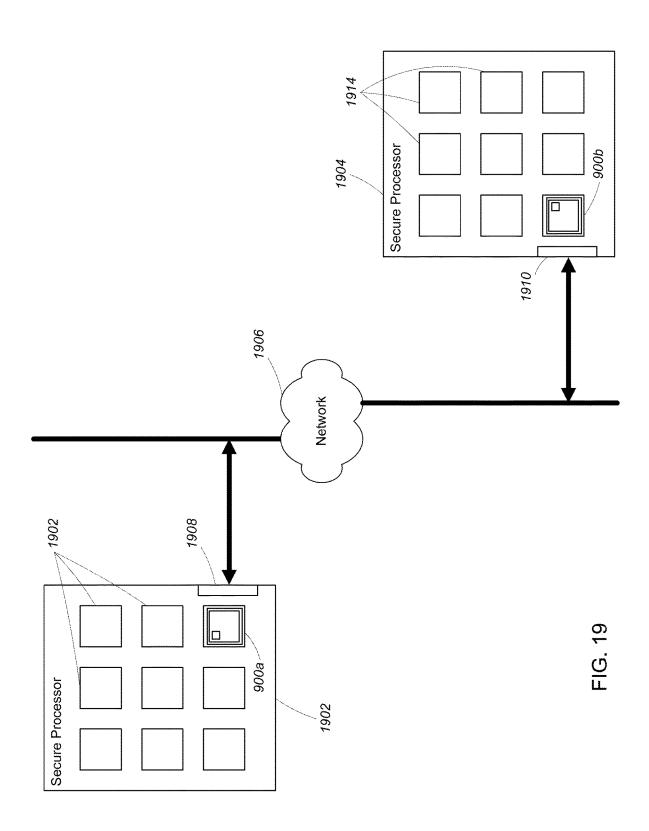

FIG. 19 is a secure processing application of a key management and cryptography device.

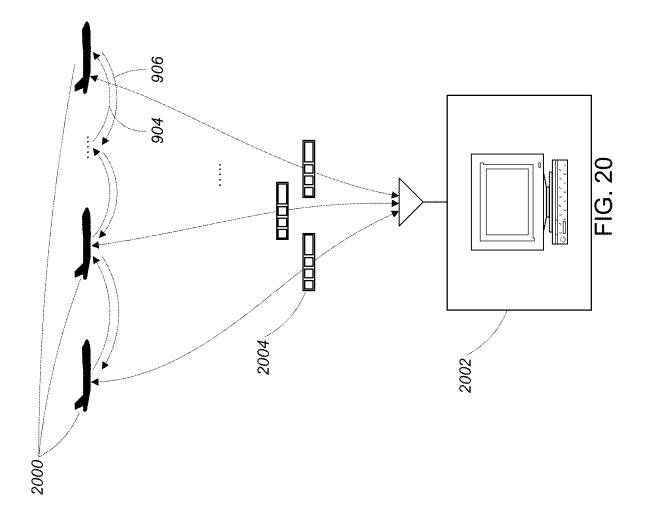

FIG. 20 is an unmanned aerial vehicle (UAV) group keying application of a key management and cryptography device.

#### DESCRIPTION

The description below focuses on a security architecture for an integrated device that incorporates cryptographic and key management functions. In some implementations, the device is a standalone device (e.g., an integrated circuit), which may be integrated with host or peripheral devices, but it should be understood that the elements described below may be further integrated, for example, in a larger monolithic device. Also, devices that are structured according to the architecture may be implemented using a variety of technologies, including but not limited to field-programmable gate arrays (FPGAs) and application-specific integrated circuits (ASICs), and may include a combination of dedicated circuitry for specific functions as well programmable embedded processing cores. Although useful functionality may be achieved using a single device, multiple devices each following the architecture may interact using the integrated cryptographic and key management functions to achieve secure communication between or distributed operation (e.g., identity management) of multiple devices, and devices following the architecture may interact with other secure systems that implement consistent security policies, but that do not necessarily themselves follow the same architecture.

At a very general level, a device following the security architecture includes multiple different security "zones." Each zone is associated with a security level, such that for at least some pairs of zones, one zone may be designated to be less secure than the other. In some examples, the security level for each zone is designated by non-negative integer index, which in this document as a matter of convention has a lower value indicating a greater degree of security (i.e., security index 0 is the most secure level), and therefore the security order of any two zones is determined by the security

indices of the zones. It should be understood that in some implementations, the zones are only partially ordered according to their security levels and therefore the relative security level of certain pairs of zones is not defined.

Each security zone has associated circuitry that imple- 5 ments functions and transformations of data within that zone. Although circuitry implementing the functions within a circuit zones may be physically separated in the layout of a particular device, logical separation of the zones is a primary factor that permits verification of the design of a 10 particular device as satisfying a security policy. In some examples, logical separation means that none of the circuitry related to data paths of a given security zone is connected to the circuitry related to data paths of another security zone except rigorously verified gate circuitry. Such logical sepa- 15 ration may be verified, for example, using automated tools using a hardware description language (HDL) specification of the circuitry without necessarily making use of a layout of that circuitry on a device. Furthermore, various types of circuitry may be used to implement functions within any 20 particular zone. For example, both dedicated logic circuitry and instruction (e.g., software) based processors may be used within any particular zone, as long as the inter-zone communication follows the security policy as discussed

In some implementations, circuitry implementing security zones may have further separations for security or other technical considerations. For example, different security zones may operate in different clock domains with clock signals being generated independently in some zones from 30 other zones. Similarly, different security zones may operate in different power zones, thereby permitting power control within zones to control energy consumption, temperature etc., and potentially to control leakage of information between zones.

As an example of use of security zones, in some examples, information at a zone at security index 0 may include root cryptographic keys, which if exposed could compromise security of numerous systems or communication links. On the other hand, information at a security index 40 1 may include session cryptographic keys, which if exposed may compromise security of a single communication link, but may not lead to the degree of undesired access that would result from exposure of a root key.

The security architecture is based on a security policy in 45 which exchange and use of data within a particular security level (e.g., in a particular security zone) is relatively unrestricted, but exchange of information between security levels is limited to enforce the security policy. An example of a policy related to exchange of information between security levels is that a data element at one security level may not pass to a lower security (e.g., higher security index) zone unless it is suitably hashed or encrypted with a key restricted to the higher security zone.

#### 1. Hardware Functional Gates

In order to verify that a particular device follows the security policy, only a limited set of functional elements are permitted to have inputs and output that are in multiple different zones, and therefore can be thought of as "bridges" between zones or functionally "gating" communication and 60 transfer of information between zones. These elements are referred to as "Hardware Functional Gates" (HFG) or "gate circuits" below, without intending to limit any characteristic of such elements by this nomenclature. A set of HFG that have been verified to satisfy a desired security policy can 65 then be used to interconnect the otherwise isolated circuits of the security zones. Verification of the HFG can use one or

10

more of a variety of techniques including manual verification, use of formal verification procedures (e.g., proofs of correctness), and simulation or enumeration of operation of the HFG. Verification that the overall circuit satisfies the security policy is done by a static analysis of the circuitry of the device to ensure that the interconnections between zones appropriately (i.e., according to the security policies) use the HFGs, for example, using automated tools that using a hardware description language (HDL) specification of the circuitry without necessarily making use of a layout of that circuitry on a device. The HFG can be considered to be a set of "building blocks" that can be used to implement complex security procedures or protocols, such that the overall implementations can be easily verified to adhere to the security policy by virtue of appropriate use of the HFGs.

Referring to FIG. 1, one example of an HFG is an encryption HFG 102 bridging two security zones (i.e., Zone 1 104 and Zone 2 106). The encryption HFG 102 has two input interfaces and one output interface. One input (K) is for a cryptographic key, and one input (D) is for a data item. In this example, both of the input interfaces are located in the same security zone (i.e., Zone 1). The output (E) is for an encryption of the data item using the key. In this example, the output interface is located in security Zone 2 which has a lower level of security (and a higher security index) than the security zone of the input interfaces (i.e., Zone 1). Furthermore, there is a control interface 109, which may be configured to accept a signal (e.g., "go") that causes the HFG to perform its function and provides a signal (e.g., "done") indicating that the function has been completed.

The HFG has an associated security policy, which dictates allowable security indexes to which the interfaces of the HFG may be coupled. If Z(K) indicates the security index of the zone to which the key (K) input is coupled, and similarly 35 Z(D) and Z(E) indicates the zones of the data input and encryption output, respectively, then a rule for use of the HFG may be that Z(E)≥Z(K) and Z(K)≤Z(D). This rule can be paraphrased as the data D must be encrypted with a key (K) at the same or higher security level (same or lower security index), and the encryption of the data E may be provided by the HFG to a zone at the same of lower security level (higher security index) as the zone of the key input.

As introduced above, an overall circuit design is verified to adhere to a security policy if the circuit topology can be divided into separate zones (i.e., circuit subgraphs of possible data flow) with the only linkages for possible data flow between zones being restricted to HFGs whose interface circuits are coupled to particular zones consistent with their security policies.

In general, each security zone has distinct memory for use within the zone and for providing inputs to and storing outputs from the HFG. In some examples, the memories of the zones include an addressable memory block of volatile memory. In some examples in which an HFG is designed to use the memories in the zones it interfaces with, the control interface to the HFG accepts a command that identifies the address(es) of the inputs and outputs. For instance, for the encryption HFG discussed above, rather than the control interface simply accepting a "go" and providing a "done" signal, the control interface may accept an input address for each of the key and data inputs, and an output address for the encrypted output. Note that these addresses are interpreted in the zones associated with the corresponding interfaces. At least conceptually each zone can be considered to have its own address space that is only accessible from circuitry within that zone or from interfaces assigned to that zone. In some cases, the control interface may accept parameters for

the function (e.g., in addition to addresses). For example, a length of a data block to be encrypted may be provided to the HFG (e.g., "encrypt a block of n bytes at address addr1 using a key at addr2, and save the result in a block of memory at address addr3"). In some examples, circuitry in a zone may 5 be implemented using a bus-based architecture in which each of the HFG and a memory block in the zone, as well as other intra zone circuitry or processing units, are on a common zone-specific bus, which supports the read and write memory operations in the address space for that zone. 10

Referring to FIGS. 2-7, an example of a non-exhaustive set of HFGS that can be used to implement a variety of devices includes a first embodiment of an encryption HFG, a controlled transfer HFG, a second embodiment of an encryption HFG, a decryption HFG, a signing HFG, a secure 15 hash HFG, and a public key generation HFG.

#### 1.1 First Encryption HFG

Referring to FIG. 2, the first embodiment of the encryption HFG 202 (which is similar to the encryption HFG 102 of FIG. 1) is shown bridging a first security zone (i.e., Zone 20 1) 204 and a second security zone (i.e., Zone 2) 206. The encryption HFG 202 is configured to encrypt a data item (D) stored in the first security zone 204 using an encryption key (K) stored in the first security zone 204 to produce an encrypted data item  $E_K(D)$  which it stores in the second 25 security zone 206. Different instances of such an encryption HFG may implement symmetric encryption (e.g., AES) or asymmetric encryption (e.g., RSA) procedures. The encryption HFG 202 has an associated security policy. The security policy ensures that no secret information (e.g., the encryption key or plaintext D) is inadvertently transferred from the first security zone 204 to the second security zone 206 through the encryption HFG 202. The security policy also ensures that the encryption HFG 202 does not allow data from lower security zones to be arbitrarily placed into higher 35 security zones and later (inadvertently or maliciously) used as a key to exfiltrate other keys or data from the higher security zones into the lower security zones. As is described above, the security policy for any encryption HFG 202 is specified such that the data item D must be encrypted with 40 a key (K) at the same or higher security level (same or lower security index), and the encryption of the data  $E_{\kappa}(D)$  may be provided by the HFG to a zone at the same or lower security level (higher security index) as the zone of the key input. As was noted above, this security policy can be concisely stated 45 as:  $Z(E) \ge Z(K)$  and  $Z(K) \le Z(D)$ . The first embodiment of the encryption HFG 202 complies with the security policy since encryption of the data E is provided by the HFG to a zone (i.e, Zone 2) with a lower security level (higher security index) than the zone (i.e., Zone 1) of the key input and the 50 data item D is encrypted with an encryption key K at a zone (i.e., Zone 1) having the same security level (the same security index) as the zone (i.e, Zone 1) associated with the data item (i.e., Z(E)>Z(K) and Z(K)=Z(D)).

To receive input data, the encryption HFG 202 includes a 55 data item input interface 203 and an encryption key input interface 205 both located in the first security zone 204. To provide output data, the encryption HFG 202 includes an encrypted data item output interface 207 located in the second security zone 206. The data item input interface 203 and the encryption key input interface 205 are connected to a Zone 1 memory 212 via a Zone 1 bus 208. The encrypted data item output interface 207 is connected to a Zone 2 memory 214 via a Zone 2 bus 210.

In some examples, the encryption HFG **202** includes a 65 control interface **209** which receives commands from a controller (not shown). In one exemplary operation of the

encryption HFG 202, the control interface 209 receives a command from the controller instructing the encryption HFG 202 to encrypt a data item (D) at a first address, addr1, in the Zone 1 memory 212 using an encryption key (K) at a second address, addr2, in the Zone 1 memory 212 and to store the resulting encrypted data item ( $E_K(D)$ ) at a third address, addr3, in the Zone 2 memory 214.

12

The command causes the encryption HFG 202 to read the data item from addr1 of the Zone 1 memory 212 and the encryption key from addr2 of the Zone 1 memory 212 via the Zone 1 bus 108. In some examples, the encryption HFG 202 reads the data item and the encryption key from the Zone 1 memory 212 in parallel. In other examples, the data item and the encryption key are sequentially read from the Zone 1 memory 212 and stored (e.g. latched) by the encryption HFG 202. Once the encryption HFG 202 receives the data item and the encryption key at their respective input interfaces 203, 205, the encryption HFG 202 applies an encryption algorithm (e.g., the Advanced Encryption Standard (AES) encryption algorithm) to encrypt the data item using the encryption key. The encryption HFG 202 stores the resulting encrypted data item at addr3 of the Zone 2 memory 214 via the Zone 2 bus 210.

Since the encryption HFG 202 conforms to the security policy described above and includes verified hardware which does not allow leakage of protected information between zones, it is impossible or exceedingly difficult for an attacker to determine the encryption key or other protected information by probing the encryption HFG 202. It is also impossible or exceedingly difficult for an attacker to use the encryption HFG 202 to arbitrarily place data from lower security zones into higher security zones such that the data can later (inadvertently or maliciously) be used as a key to exfiltrate other keys or data from the higher security zones into the lower security zones.

#### 1.2 Controlled Transfer HFG

Referring to FIG. 3, the controlled transfer HFG 316 (sometimes referred to as a "controlled transfer gate") is shown bridging a first security zone (i.e., Zone 1) 304 and a second security zone (i.e., Zone 2) 306, the first security zone 304 having a higher level of security than the second security zone 306. The controlled transfer HFG 316 is configured to retrieve a data item (D) from the second security zone 306 and to store the data item, unmodified, in the first security zone 304. The controlled transfer HFG 316 has an associated security policy. The security policy ensures that no secret information (e.g., the private key) is inadvertently transferred from the first security zone 804 to the second security zone 806 through the controlled transfer HFG 316. The security policy for the controlled transfer HFG 316 is specified such that the security level of the zone from which the data item is read must be lower than the security level of the zone from which the data item is written out. The security policy for the controlled transfer HFG 316 can be concisely stated as:  $Z(D_{Out})>Z(D_{In})$ .

To receive the data item as input, the controlled transfer HFG 316 includes a data item input interface 318 located in the second security zone 306 and connected to a Zone 2 memory 314 via a Zone 2 bus 310. To provide the data item as output, the controlled transfer HFG 316 includes a data item output interface 320 located in the first security zone 304 and connected to a Zone 1 memory 312 via a Zone 1 bus 308.

In some examples, the controlled transfer HFG 316 includes a control interface 309 which receives commands from a controller (not shown). In one exemplary operation of the controlled transfer HFG 316, the control interface 309

receives a command from the controller instructing the controlled transfer HFG 316 to retrieve a data item (D) from a first address, addr1, in the Zone 2 memory 314 and transfer the data item to a second address, addr2, in the Zone 1 memory 312. The command causes the controlled transfer 5 HFG 316 to read the data item from addr1 of the Zone 2 memory 314 via the Zone 2 bus 310. Once the controlled transfer HFG 316 receives the data item, the controlled transfer HFG 316 writes the data item, without modification, to addr2 of the Zone 1 memory 312 via the Zone 1 bus 308. 10

Since the controlled transfer HFG 316 conforms to the security policy described above and includes verified hardware which does not allow leakage of protected information between zones, it is impossible or exceedingly difficult for an attacker to access information in Zone 1 304 by probing 15 the controlled transfer HFG 316.

In some examples, the controlled transfer HFG 316 includes logic which analyzes the data item (D) to determine whether it meets certain conditions (e.g., length, format, or rate conditions). If it is determined that the data item does 20 not meet the conditions, then the controlled transfer HFG 316 does not transfer the data item into the first security

In other examples, the controlled transfer HFG 316 includes logic which allows only a single data item to be 25 transferred through the HFG. For example, the HFG may maintain a bit representing whether a data item has yet been transferred though the HFG. Before any data item has been transferred through the HFG, the value of the bit is set to 0. When a request to transfer a data item is received at the 30 controlled transfer HFG, the value of the bit is read. If the value of the bit is 0, data transfer is permitted. Upon transferring a data item through the controlled transfer HFG, the value of the bit is set to 1. If the value of the bit is 1, data transfer is not permitted. Thus, after a single data item is 35 transferred through the controlled transfer HFG, any subsequent attempts to transfer data through the controlled transfer HFG are not permitted due to the value of the bit being set to 1. In this way, the controlled transfer HFG logic prevents data from lower security zones from being arbi- 40 trarily placed into higher security zones and later (inadvertently or maliciously) be used as a key to exfiltrate other keys or data from the higher security zones into the lower security zones.

In some examples, the controlled transfer HFG is used to 45 place the data item (D) into a designated staging area where other HFGs have access to the data item. In some examples, the designated staging areas include memory which is separate from the memory in which keys are stored.

1.3 Second Encryption HFG

Referring to FIG. 4 a second embodiment of an encryption HFG 422 is shown bridging a first security zone (i.e., Zone 1) 404 and a second security zone (i.e., Zone 2) 406. The encryption HFG **422** is configured to encrypt a data item tion key (K) stored in the first security zone 404 to produce an encrypted data item  $E_{\kappa}(D)$  which it stores in the second security zone 406. To ensure that no secret information (e.g., the private key) is inadvertently transferred from the first security zone 404 to the second security zone 406 through 60 the encryption HFG 422, encryption HFG 422 complies with the general encryption HFG security policy described above. In particular, the encryption HFG 422 complies with the general encryption HFG security policy since the encryption of the data item  $E_K(D)$  is provided by the 65 encryption HFG 422 to a zone with a lower security level (higher security index) than the zone of the key input and the

14

data item D is encrypted with an encryption key K at a zone having a higher security level (a lower security index) than the zone associated with the data item (i.e., Z(E)>Z(K) and Z(K) < Z(D)).

To receive input data, the encryption HFG 422 includes a data item input interface 403 located in the second security zone 406 and an encryption key input interface 405 located in the first security zone 404. To provide output data, the encryption HFG 422 includes an encrypted data item output interface 407 located in the second security zone 406. The data item input interface 403 and the encrypted data item output interface 407 are connected to a Zone 2 memory 414 via a Zone 2 bus 408. The encryption key input interface 405 is connected to a Zone 1 memory 412 via a Zone 1 bus 408.

Internally, an example of the second embodiment of the encryption HFG 422 includes the first embodiment of the encryption HFG 402 of FIG. 2 and the controlled transfer HFG 416 of FIG. 3. The controlled transfer HFG 416 is used to transfer the data item D from Zone 2 406 into Zone 1 404 for encryption using the first embodiment of the encryption HFG 402. Specifically, the data item input interface 403 of the second embodiment of the encryption HFG 422 is connected to the data item input 418 of the controlled transfer HFG 416 in Zone 2. The data item output interface 420 of the controlled transfer HFG 416 is connected to the data item input interface 403' of the first embodiment of the encryption HFG 402. The encryption key input interface 405 of the second embodiment of the encryption HFG 422 is connected to the encryption key input interface 405' of the first embodiment of the encryption HFG 402. The encrypted data item output interface 407' of the first embodiment of the encryption HFG 402 is connected to encrypted data output interface 407 of the second embodiment of the encryption HFG 422. Of course, not all implementations make use of such an internal arrangement, for example, using an optimized circuit that achieves the same functionality and data protection.

In some examples, the second embodiment of the encryption HFG 422 includes a control interface 409 which receives commands from a controller (not shown) and provides the commands to a control interface 409' of the first embodiment of the encryption HFG 402 and to a control interface 411 of the controlled transfer HFG 416. In one exemplary operation of the encryption HFG 422, the control interface 409 receives a command from the controller instructing the encryption HFG 422 to encrypt a data item (D) at a first address, addr1, in the Zone 2 memory 414 using an encryption key (K) at a second address, addr2, in the Zone 1 memory 412 and to store the resulting encrypted data item  $(E_{\kappa}(D))$  at a third address, addr3, in the Zone 2 memory

The command causes the controlled transfer HFG 416 to (D) stored in the second security zone 406 using an encryp- 55 read the data item (D) from addr1 of the Zone 2 memory 414 via the Zone 2 bus 410. Once the controlled transfer HFG 416 receives the data item, the controlled transfer HFG 416 provides the data item, without modification, to the data item input interface 403' of the first embodiment of the encryption HFG 402. The command also causes the first embodiment of the encryption HFG 402 to read the encryption key (K) from addr2 of the Zone 1 memory 412 via the Zone 1 bus 408. Once the first embodiment of the encryption HFG 402 receives the data item and the encryption key at their respective input interfaces 403', 405' the first embodiment of the encryption HFG 402 applies an encryption algorithm to encrypt the data item using the encryption key. The first

embodiment of the encryption HFG 202 stores the resulting encrypted data item  $E_K(D)$  at addr3 of the Zone 2 memory via the Zone 2 bus 410.

Since the second embodiment of the encryption HFG 422 and its component parts (i.e., the first embodiment of the encryption HFG 402 and the controlled transfer HFG 416) all conform to the encryption security policy described above and include verified hardware which does not allow leakage of encryption key information between zones, it is impossible or exceedingly difficult for an attacker to determine the encryption key or other protected information by probing the second embodiment of the encryption HFG 422. It is also impossible or exceedingly difficult for an attacker to use the encryption HFG 422 to arbitrarily place data from lower security zones into higher security zones such that the data can later (inadvertently or maliciously) be used as a key to exfiltrate other keys or data from the higher security zones into the lower security zones.

#### 1.4 Decryption HFG

Referring to FIG. 5, the decryption HFG 524 is shown bridging a first security zone (i.e., Zone 1) 504 and a second security zone (i.e., Zone 2) 506, the first security zone 504 having a higher level of security than the second security zone 506. The decryption HFG 524 is configured to decrypt 25 an encrypted data item ( $E_K(D)$ ) stored in the second security zone 506 using an encryption key (K) stored in the first security zone 504 to produce an unencrypted data item (D) which it stores in the first security zone 504.

The decryption HFG 524 has an associated security 30 policy. The security policy ensures that no secret information (e.g., the private key) is inadvertently transferred from the first security zone 504 to the second security zone 506 through the decryption HFG 524. The security policy also ensures that the decryption HFG 524 does not allow data 35 from lower security zones to be arbitrarily placed into higher security zones and later (inadvertently or maliciously) used as a key to exfiltrate other keys or data from the higher security zones into the lower security zones. The security policy for the decryption HFT 524 is specified such that an 40 encrypted data item  $(E_K(D))$  must be decrypted with an encryption key (K) at the same or higher security level (same or lower security index) and the decrypted data item (D) must be provided to a zone at the same security level (security index) as the zone of the encryption key. This 45 security policy can be concisely stated as:  $Z(E) \ge Z(K)$  and Z(K)=Z(D)).

To receive input data, the decryption HFG **524** includes an encrypted data item input interface **526** located in the second security zone **506** and connected to a Zone 2 memory **514** 50 via a Zone 2 bus **510** and an encryption key input **505** located in the first security zone **504** and connected to a Zone 1 memory **512** via a Zone 1 bus **508**. To provide a decrypted data item output, the decryption HFG **524** includes a data item output interface **528** located in the first security zone **55 504** and coupled to the Zone 1 memory **514** via the Zone 1 bus **508**

In some examples, the decryption HFG **524** includes a control interface **509** which receives commands from a controller (not shown). In one exemplary operation of the 60 decryption HFG **52**, the control interface **509** receives a command from the controller instructing the decryption HFG **524** to decrypt an encrypted data item ( $E_K(D)$ ) at a first address, addr1, in the Zone 2 memory **514** using an encryption key (K) at a second address, addr2, in the Zone 1 65 memory **512** and to store the resulting decrypted data item (D) at a third address, addr3, in the Zone 1 memory **512**.

16

The command causes the decryption HFG 524 to read the encrypted data item from addr1 of the Zone 2 memory 514 via the Zone 2 bus 510 and to read the encryption key from addr2 in the Zone 1 memory 512 via the Zone 1 bus 508. Once the decryption HFG 524 receives the encrypted data item and the encryption key at their respective input interfaces 526, 505, the decryption HFG 524 applies a decryption algorithm (e.g., the AES decryption algorithm) to decrypt the encrypted data item using the encryption key. The decryption HFG 524 stores the resulting decrypted data item at addr3 of the Zone 1 memory 514 via the Zone 1 bus 508.

Since the decryption HFG **524** conforms to the security policy described above and includes verified hardware which does not allow leakage of the encryption key or other protected information between zones, it is impossible or exceedingly difficult for an attacker to determine the encryption key or other protected information by probing the decryption HFG **524**. It is also impossible or exceedingly difficult for an attacker to use the decryption HFG **524** to arbitrarily place data from lower security zones into higher security zones such that the data can later (inadvertently or maliciously) be used as a key to exfiltrate other keys or data from the higher security zones into the lower security zones.

Note that together, an encryption, for example HFG **202** (see FIG. **2**), and a decryption HFG **524** (see FIG. **5**) provide a means to export a data item D from a secure zone (i.e., zone 1) as an encrypted (e.g., opaque) data item  $E_K(D)$ , which may be stored in a non-secure location, and then later imported back to the same zone, or any other zone (e.g., a zone 1 at another device), which holds the matching key K used to decrypt the data item.

#### 1.5 Signing HFG

Referring to FIG. 6, the signing HFG 634 is shown bridging three security zones: a first security zone (i.e., Zone 0) 633, a second security zone (i.e., Zone 1) 604, and a third security zone (i.e., Zone 2) 606. The first security zone 633 has a higher level of security than the second security zone 604 which in turn has a higher security level than the third security zone 606.

The signing HFG 634 is configured to digitally sign a data item (D) stored in the second security zone 604 using a cryptographic key (K) stored in the first security zone 633 and a random number (R) to produce a signature of the data item (S(D)) which it stores in the third security zone 606. When a device including the signing HFG 634 sends the signed data item to a receiver, the receiver can verify the signature to ensure that the data is authentic and from the device.

The signing HFG **634** has an associated security policy. The security policy ensures that no secret information (e.g., the private key) is inadvertently transferred from the first security zone 633 to the second security zone 604 or third zone 606 through the signing HFG 634. The security policy also ensures that the signing HFG 634 does not allow data from lower security zones to be arbitrarily placed into higher security zones and later (inadvertently or maliciously) used as a key to exfiltrate other keys or data from the higher security zones into the lower security zones. The security policy for the signing HFG 634 is specified such that a data item (D) must be signed using a key (K) from the same or higher security level and the signature of the data item (S(D)) may be provided to a zone at the same or lesser security level as the zone of the encryption key. This security policy can be concisely stated as:  $Z(S) \ge Z(K)$  and  $Z(K) \le Z$ (D)

To receive input data, the signing HFG 634 includes a cryptographic key input interface 605 located in the first

security zone 633, a random value interface 607 located in the first security zone 633, and a data item input interface 603 located in the second security zone 604. To provide output data, the signing HFG 634 includes a signed data output interface 628 located in the third security zone 606. 5 The cryptographic key input interface 605 is connected to a Zone 0 memory 630 via a Zone 0 bus 632. The data item interface 603 and the random value interface 607 are connected to a Zone 1 memory 612 via a Zone 1 bus 608. The signed data output interface 628 is connected to a Zone 2 10 memory 614 via a Zone 2 bus 610.

In some examples, the signing HFG 634 includes a control interface 609 which receives commands from a controller (not shown). In one exemplary operation of the signing HFG 634, the control interface 609 receives a 15 command from the controller instructing the signing HFG 634 to sign a data item (D) at a first address, addr1, in the Zone 1 memory 612 using a random value (R) at a fourth address, addr4, in Zone 1 memory and a signing key (K) at a second address, addr2, in the Zone 0 memory 630 and to 20 control interface 709 which receives commands from a store the resulting signed data item (S(D)) at a third address, addr3, in the Zone 2 memory 214.

The command causes the signing HFG 634 to read the data item from addr1 of the Zone 1 memory 612 via the Zone 1 bus **608**, to read the random value from addr4 of the Zone 25 1 memory 612 via the Zone 1 bus 608, and to read the signing key from addr2 of the Zone 0 memory 630 via the Zone 0 bus 632. Once the signing HFG 202 receives the data item, the random value, and the cryptographic key at their respective input interfaces 603, 605, the signing HFG 634 30 applies a digital signing algorithm (e.g., the Elliptic Curve Digital Signing Algorithm (ECDSA)) to sign the data item using the signing key. The signing HFG 634 stores the resulting signed data item S(D) at addr3 of the Zone 2 memory 614 via the Zone 2 bus 610.

Since the signing HFG 634 conforms to the security policy described above (i.e., Z(S)>Z(K) and Z(K)<Z(D)) and includes verified hardware which does not allow leakage of encryption key information between zones, it is impossible or exceedingly difficult for an attacker to determine the 40 cryptographic key or other protected information by probing the signing HFG 634. It is also impossible or exceedingly difficult for an attacker to use the signing HFG 634 to arbitrarily place data from lower security zones into higher security zones such that the data can later (inadvertently or 45 maliciously) be used as a key to exfiltrate other keys or data from the higher security zones into the lower security zones.

Similar to the signing HFG 634, another HFG that is not illustrated performs a signature verification, for example accepting a purported signature S rather than providing it as 50 with the signing HFG, and providing a control signal to the same zone as the signature indicating whether the signature is valid based on the data D and key K at the same or higher security zones.

#### 1.6 Secure Hash HFG

Referring to FIG. 7, the secure hash (SHA) HFG 736 is shown bridging a first security zone (i.e., Zone 1) 704 and a second security zone (i.e., Zone 2) 706, the first security zone 704 having a higher level of security than the second security zone 706. The secure hash HFG 736 is configured 60 to securely hash a data item (D) stored in the first security zone 704 and store the secure hash of the data item (H) in the second security zone 706.

The secure hash HFG 736 has an associated security policy. The security policy ensures that no protected infor- 65 mation is inadvertently transferred from the first security zone 704 to the second security zone 706 through the secure

hash HFG 736. The security policy also ensures that the secure hash HFG 736 does not allow data from lower security zones to be arbitrarily placed into higher security zones and later (inadvertently or maliciously) used as a key to exfiltrate other keys or data from the higher security zones into the lower security zones. The security policy is specified such that the secure hash of the data item H may be provided to a security zone with the same or lower security level (higher security index) as the zone of the data item. This security policy can be concisely stated as:  $Z(H) \ge Z(D)$

18

To receive the data item as input, the secure hash HFG 736 includes a data item input interface 703 located in the first security zone 704 and connected to a Zone 1 memory 712 via a Zone 1 bus 710. To provide the secure hash of the data item as output, the secure hash HFG 736 includes a secure hash output interface 738 located in the second security zone 706 and connected to a Zone 2 memory 714 via a Zone 2 bus 710.

In some examples, the secure hash HFG 736 includes a controller (not shown). In one exemplary operation of the secure hash HFG 736, the control interface 709 receives a command from the controller instructing the secure hash HFG **736** to perform a secure hash operation on a data item (D) at a first address, addr1, in the Zone 1 memory 712 and to store the resulting securely hashed data item (H) in a second address, addr2, in the Zone 2 memory 714.

The command causes the secure hash HFG 736 to read the data item from addr1 of the Zone 1 memory 712 via the Zone 1 bus 708. Once the secure hash HFG 736 receives the data item at its data item input interface 703, the secure hash HFG 736 applies a secure hash function to the data item, resulting in a secure hash of the data item. The secure hash HFG 736 stores the resulting secure hash of the data item at addr2 of 35 the Zone 2 memory 714 via the Zone 2 bus 710.

Since the secure hash HFG 736 conforms to the security policy described above (i.e., Z(H)>Z(D)) and includes verified hardware which does not allow leakage of information (e.g., the data item) between zones, it is impossible or exceedingly difficult for an attacker to determine the data item or other protected information by probing the secure hash HFG 736. It is also impossible or exceedingly difficult for an attacker to use the secure hash HFG 736 to arbitrarily place data from lower security zones into higher security zones such that the data can later (inadvertently or maliciously) be used as a key to exfiltrate other keys or data from the higher security zones into the lower security zones. 1.7 Public Key Generation HFG

Referring to FIG. 8, the public key generation HFG 840 is shown bridging a first security zone (i.e., Zone 1) 804 and a second security zone (i.e., Zone 2) 806, the first security zone 804 having a higher level of security than the second security zone 806. The public key generation HFG 840 is configured to retrieve a private key  $(K_{Pr})$  from the first security zone 804 and to use the private key to generate a corresponding public key  $(K_{Pu})$  which it stores in the second security zone 806.

The public key generation HFG 840 has an associated security policy. The security policy ensures that no secret information (e.g., the private key) is inadvertently transferred from the first security zone 804 to the second security zone 806 through the public key generation HFG 840. The security policy also ensures that the public key HFG 840 does not allow data from lower security zones to be arbitrarily placed into higher security zones and later (inadvertently or maliciously) used as a key to exfiltrate other keys or data from the higher security zones into the lower security

zones. The security policy for the public key generation HFG **840** is specified such that the public key generated by the public key generation HFG **840** may be provided by the HFG to a zone at the same or lower security level (higher security index) as the private key. The security policy for the 5 public key generation HFG **840** can be concisely stated as:  $Z(K_{Pu}) \ge Z(K_{Pr})$ .

19

To receive the private key as input, the public key generation HFG **840** includes a private key input interface **842** located in the first security zone **804** and connected to a Zone 1 memory **812** via a Zone 1 bus **808**. To provide the generated public key as output, the public key generation HFG **840** includes a public key output interface **844** located in the second zone **806** and connected to a Zone 2 memory **814** via a Zone 2 bus **810**.

In some examples, the public key generation HFG **840** includes a control interface **809** which receives commands from a controller (not shown). In one exemplary operation of the public key generation HFG **840**, the control interface **890** receives a command from the controller instructing the 20 public key generation HFG **840** to generate a public key from a private key at a first address, addr1, in the Zone 1 memory **812** and to store the generated public key at a second address, addr2, in the Zone 2 memory **814**.

The command causes the public key generation HFG **840** 25 to read the private key ( $K_{P_P}$ ) from addr1 of the Zone 1 memory **812** via the Zone 1 bus **808**. Once the public key generation HFG **840** receives the private key at its private key input interface **842**, the public key generation HFG **840** uses the private key to generate a public key (e.g., an 30 ephemeral public key). The public key generation HFG **840** stores the resulting public key at addr2 of the Zone 2 memory **814** via the Zone 2 bus **810**.

Since the public key generation HFG **840** conforms to the security policy described above (i.e.,  $Z(K_{Pu}) > Z(K_{Pr})$ ) and 35 includes verified hardware which does not allow leakage of information (e.g., the private key) between zones, it is impossible or exceedingly difficult for an attacker to determine the private key or other protected information by probing the public key generation HFG **634**. It is also 40 impossible or exceedingly difficult for an attacker to use the public key generation HFG **840** to arbitrarily place data from lower security zones into higher security zones such that the data can later (inadvertently or maliciously) be used as a key to exfiltrate other keys or data from the higher security zones 45 into the lower security zones.

While the set of HFGs described above may be sufficient for implementation of some devices, other devices may include additional types of HFGs for securely communicating between security zones.

In the examples described above, HFGs were shown bridging either two or three security zones. However, it is noted that a given HFG can bridge a greater or fewer number of security zones as long as its security policy is observed. 1.8 Other Circuit Elements

The library of HFG defined to implement a security policy is optionally extended to include elements that may be used exclusively within one zone. For example, a secure hash element does not necessarily have to be used to bridge zones, and may be used exclusively within one zone. Also, 60 some elements, such as a true random number generator or a pseudo-random number generator may be included in the library only for use within a single zone.

In the discussion above, and below, HFGs instances may be shown as distinct even if they implement the same 65 function and have the interfaces in the same zones. In such cases, these instances may be implemented in the device as 20

a single shared circuit element, for example, multiplexing and demultiplexing different inputs and outputs for different operations. Note however, that such multiplexing cannot be implemented in a manner that would violated the policy regarding passing data between zones.

#### 1.9 Logical Functional Gates

In some implementations, in addition to the HFG, which enforce the security policy by virtue of the functions that are possible to implement according to the circuitry, additional gate elements may be verified to provide logical security in that data security may be enforced if the element is suitably controlled (e.g., the logic implemented for the controlled transfer HFG described above). Such elements are referred to as "logical functional gates". Note that although using such logical gates between zones may provide a degree of security assuming that the logical control of the elements is not compromised for example by errors in implementation, such logical gates are not used between zones where a strict security policy is to be enforced and verified by the static hardware analysis.

#### 2. Key Management and Cryptography Device

Referring to FIG. 9, one example of a key management and cryptography device 900 utilizes the HFGs described above to manage cryptographic keys and perform cryptographic tasks (e.g., create various keys for various purposes, associate meta-data with the keys, use cryptographic functions to protect application data using the keys, and so on). The device can also protect keys (and meta-data) at rest and securely wrap keys (with their meta-data) to other compatible devices. In some examples, such a device is used as part of a larger system which requires key management and cryptography services.

The example device 900 includes four security zones each associated with a security index. In general, a lower the security index denotes a higher the level of security. That is, Zone 0 (i.e., the security zone associated with security index 0) has the highest level of security and Zone 3 (i.e., the security zone associated with security index 3) has the lowest level of security. With the exception an initial "unlocking" procedure (described below), all transfer of data between zones (e.g., from zones with lower security indices to zones with higher security indices) must be performed through HFGs.

In general, Zones 0-3 each includes a memory and a bus. That is, Zone 0 933 includes a Zone 0 memory 930 and a Zone 0 bus 932, Zone 1 904 includes a Zone 1 memory 912 and a Zone 1 bus 908, and Zone 2 includes a Zone 2 memory 914 and a Zone 2 bus 910. HFGs and other hardware modules with interfaces in a given zone can access the zone's memory via the zone's bus. The bus may also communicate control information to and from HFGs and other hardware modules. Such control information may originate, for example, from a microcontroller (e.g., a Tensilica processor in Zone 3) or from a zone specific controller. In general, for the sake of simplicity, control information paths are not illustrated in the figures.

Zone 0 has the highest level of security and is used to store critical data such as root keys and digital signing keys. To maintain the highest level of security, the number of HFGs bridging the boundary of Zone 0 is minimal. Zone 1 is somewhat less secure than Zone 0. Zone 1 has a greater number of HFGs bridging its boundaries, some of which have interfaces in less secure Zones 2 and 3. In general, Zone 1 is used to perform the majority of functions related to provisioning the device, unlocking the device, session key generation, generation and unwrapping of keywrap data, and so forth. Zone 2 generally acts as an interface and staging

area between custom code running in Zone 3 and the more secure zones. For example, Zone 2 may store a keywrap in the Zone 2 memory **914** such that Zones 0 and 1 can access the keywrap.